Akeana is a venture funded, RISC-V, startup founded in early 2021 by leaders in the industry. Our semiconductor IP offerings include low-end microcontroller cores, mid-range embedded cores, and high-end laptop/server cores, along with coherent and non-coherent interconnects and accelerators.

Akeana was founded with the goal of bringing maximum performance and capabilities to the RISC-V ecosystem. The team is leveraging its vast experience, such as working on successful projects like ThunderX at Cavium/Marvell, to bring you best-in-class CPU and System IP.

We license a complete suite of RISC-V Core IP – including microcontrollers, Big-Little application cores, high performance data center cores, as well as multi-threaded cores for networking and other high throughput applications. The highly configurable design methodology also allows Akeana to provide cores optimized for specific vertical markets and applications. In addition to cores, Akeana provides a complete suite of system IP including cluster caches, non-coherent interconnects (AXI), coherent interconnects (CHI), RISC-V interrupt controllers, RISC-V IOMMU, security IP, and AI accelerators.

© Copyright Akeana 2024

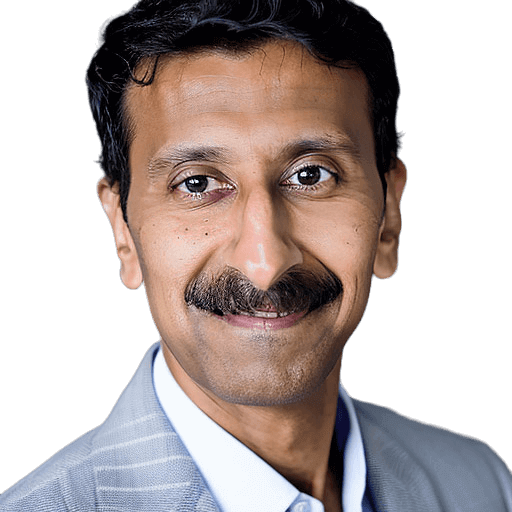

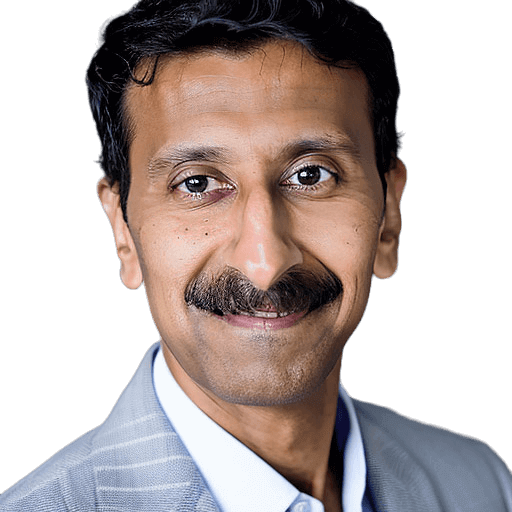

Rabin Sugumar was Distinguished Engineer and Chief Architect at Marvell/Cavium and built and led the architecture group for the ThunderX Arm server processor line. Most recently he led the architecture of the ThunderX3 processor, which had industry leading single thread performance and socket level performance at time of silicon. Prior to Marvell/Cavium, he was at Broadcom where he was one of the lead architects on the server processor that became ThunderX2. ThunderX2 was the first Arm server to achieve single thread and socket level performance comparable to high end Intel Xeon servers and paved the way for Arm servers in the data center. During Rabin’s career, he has also worked on architecture and design of vector processors at Cray Research, early multi-threaded and out-of-order SPARC processors at Sun Microsystems, and InfiniBand adapters at Sun Microsystems/Oracle. Rabin obtained his PhD in Computer Science and Engineering from the University of Michigan. The cache simulator he wrote during his PhD is still widely used in academia. Rabin has over 25 years of experience in CPU architecture and design, and 28 granted patents.

Nitin Rajmohan is a design verification leader and has a long track record of building large multi-site validation teams, validating complex cores, and producing high quality silicon. Most recently, Nitin was the Senior Director of Verification on the Arm server program at Marvell and led core validation on the ThunderX3 program. Prior to ThunderX3 Nitin led core validation on ThunderX2 at Broadcom and later Cavium and Marvell. Nitin also led the post-silicon validation effort on ThunderX2 and was part of the team that successfully delivered ThunderX2 for the Astra Supercomputer – the first Arm based system to feature in the Top500 Supercomputers. Nitin has also led core validation on MIPS based designs at Broadcom/Netlogic and worked on x86 validation at Intel.

Abbas Rashid has led design and development teams for several successful chips over the course of his career. Most recently Abbas was the Director of Logic design on the ThunderX Arm server program at Marvell, where he led design for the CPU Core, Memory Subsystem, and DFT. Before Marvell, Abbas was at Broadcom/Netlogic as head of the Core CPU Design team. The team delivered the industry’s highest performance embedded MIPS-based multi-core processor. Subsequently, after the product transitioned to Arm from MIPS, the core team lead by him delivered the industry’s highest performance Arm server processor and next generation multi-core solution. Abbas has over 25 years of experience in CPU design and over 25 granted patents.

Syed co-founded Cavium Networks, where he served as President, CEO, and Chairman of the Board. Syed’s timely vision and leadership in secure high-performance networking equipment enabled him to take Cavium public in 2007 (NASDAQ: CAVM), grow the company’s revenue to $1B+, and close an acquisition by Marvell Technology for $6B+. Prior to this Syed served as VP of Marketing and Sales at Malleable Technologies, where he was a founding management team member, leading to the acquisition by PMC Sierra. Mr. Ali also served as Executive Director at Samsung Electronics where he started the flash memory and CPU businesses. Syed received a BSEE from Osmania University, Hyderabad, India and an MSEE from the University of Michigan. Mr. Ali was named winner of the Ernst & Young Technology Entrepreneur of The Year 2008 award for Northern California, an award recognizing those who build and lead dynamic, growing businesses. Syed continues activities that give back to the engineering community.

Amit Nanda has held executive and senior management roles at companies that span systems-to-silicon technologies. His responsibilities have entailed marketing, business development, organic and inorganic technology incubation and strategic partnerships. Amit currently serves as the Vice President, Strategy, Solutions and Partnerships at Akeana. Before Akeana, Amit led the Advanced Technology Sourcing and Partnerships team at Google. The team helped incubate new technologies for Technical Infrastructure and worked with industry ecosystem initiatives. Amit also served as the Google representative on the CXL Consortium’s Board of Directors. Prior to this, Amit was responsible for strategy and business development supporting Azure Hardware Systems and Infrastructure at Microsoft. Earlier in his career, Amit worked in the semiconductor industry, within foundry/fabless/EDA/IP companies, serving hyperscalers, OEMs, and IC suppliers. Amit holds an MBA from Santa Clara University, a M.S. in Electrical Engineering from Colorado State University and a B.S. in Electronics Engineering from University of Bombay.

David Baker grew up on a ranch in New Mexico. He received his BSEE from New Mexico State University and his MSE and PHD in ECE from the University of Texas, Austin. His area of research interest was computer vision and image processing. He began his career on a super-computer design at Texas Instruments, competing with Cray. While there, he worked on the design of the TI TMS9900 and TMS99000 MCU chips. He joined IBM and worked on various internal processors as well as the ISA development for ROMP(801), IBM RT, and RS6000 Graphics. While working for IBM Research he was part of the original AIX hypervisor implementation team and later the GL to OpenGL ports to RS6000. Subsequently he has spent 25 years doing startups including two IPOs and two acquisitions, at places like SigmaTel, NVidia, Brooktree, and Legerity. Along the way, he was VP of engineering for 3 different VLIW DSP companies and worked on micro- architectures and ISAs for almost all of his career to date. He was Chief Architect at ETA Compute for self-timed processor products and at Luminous computing for their disaggregated memory data center ML training chip sets. This included the architecture of a domain specific VLIW vector processor for ML.

Oops! We could not locate your form.